ISL6617AFRZ-T Fazdividilo 3.3V PWMIntraportebla Logiko

♠ Produkta Priskribo

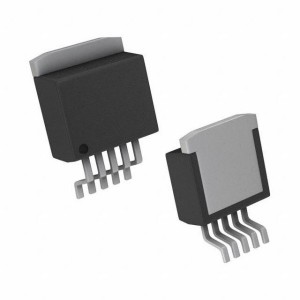

| Produkta Atributo | Atributa Valoro |

| Fabrikisto: | Renesas Elektroniko |

| Produkta Kategorio: | Ŝaltigaj Regiloj |

| RoHS: | Detaloj |

| Pakado: | Bobeno |

| Marko: | Renesas / Intersil |

| Alto: | 0.9 milimetroj |

| Longo: | 3 milimetroj |

| Humideca Sentema: | Jes |

| Produkta Tipo: | Ŝaltigaj Regiloj |

| Serio: | ISL6617 |

| Fabrikpakaĵa Kvanto: | 6000 |

| Subkategorio: | PMIC - Potencaj Administraj IC-oj |

| Larĝo: | 3 milimetroj |

| Unuopezo: | 22 mg |

♠ ISL6617A PWM Duobligilo kun Elira Monitorada Funkcio

La ISL6617A uzas la proprietan Phase Doubler-skemon de Intersil por moduli dufazajn potenco-trajnojn per ununura PWM-enigo. Ĝi duobligas la nombron de fazoj, kiujn 3,3V plurfazaj regiloj povas subteni.

La ISL6617A estas desegnita por minimumigi la nombron de analogaj signaloj, kiuj interagas inter la regilo kaj peliloj en skaleblaj aplikoj kun alta fazkalkulo. La komuna COMP-signalo, kiu kutime videblas en konvenciaj kaskadaj konfiguracioj, ne estas necesa; tio plibonigas bruimunecon kaj simpligas la aranĝon. Krome, la ISL6617A provizas malaltan partkalkulon kaj malaltkostan avantaĝon kompare kun la konvencia kaskada tekniko.

Kaskadante la ISL6617A kun alia ISL6617 aŭ ISL6611A, ĝi povas kvarobligi la nombron de fazoj, kiujn 3,3V plurfazaj regiloj povas subteni.

La ISL6617A ankaŭ havas tri-statajn enigojn kaj eligojn, kiuj rekonas alt-impedancan staton, kunlaborante kun Intersil-multifazaj PWM-regiloj kaj pelilaj stadioj por malhelpi negativajn transientojn sur la kontrolita elira tensio kiam funkciado estas haltigita. Ĉi tiu trajto forigas la bezonon de la Schottky-diodo, kiu povus esti uzata en potenca sistemo por protekti la ŝarĝon kontraŭ troa difekto de negativa elira tensio.

• Proprieta fazduobliga skemo

• Plibonigita efikeco je malpeza ĝis plena ŝarĝo

• Duobla aŭ kvarobla fazkalkulo

• Patentita kurenta ekvilibrigo kun DCR-kurenta sentado kaj alĝustigebla gajno

• Eligo de kurenta monitorado (IOUT) por simpligi la sisteman interfacon kaj aranĝon

• Tri-nivela ebliga enigo por reĝimo-elekto

• Duoblaj PWM-eligaj stiriloj por du sinkronaj rektigitaj pontoj kun ununuraPWM-enigo

• Kanala sinkronigado kaj du interplektaj opcioj

• Subteno de 3.3V PWM-enigo

• Subtenas 5V PWM-eligon • Kongrua kun DCR-sensado aŭ inteligenta potenc-ŝtupa sensado

• Tri-stata PWM-enigo kaj eligoj por malŝalto de la elira etapo

• Protekto kontraŭ trotensio

• Duobla Plata Senplumba (DFN) pakaĵo - Preskaŭ ĉip-skala pakaĵo; plibonigas PCB-utiligon, pli maldika profilo - Senplumba (RoHS-konforma)

• Alt-kurentaj, malalt-tensiaj kontinukurentaj/kontinukurentaj konvertiloj

• Altfrekvenca kaj alt-efikeca VRM kaj VRD

• Aplikoj kun alta fazkalkulo kaj fazdeŝado

• 3.3V PWM-enigo integrita potenco-stadio aŭ DrMOS