P1020NXN2HFB Mikroprocesoroj - MPU 800/400/667 ET NE r1.1

♠ Produkta Priskribo

| Produkta Atributo | Atributa Valoro |

| Fabrikisto: | NXP |

| Produkta Kategorio: | Mikroprocesoroj - MPU |

| RoHS: | Detaloj |

| Munta Stilo: | SMD/SMT |

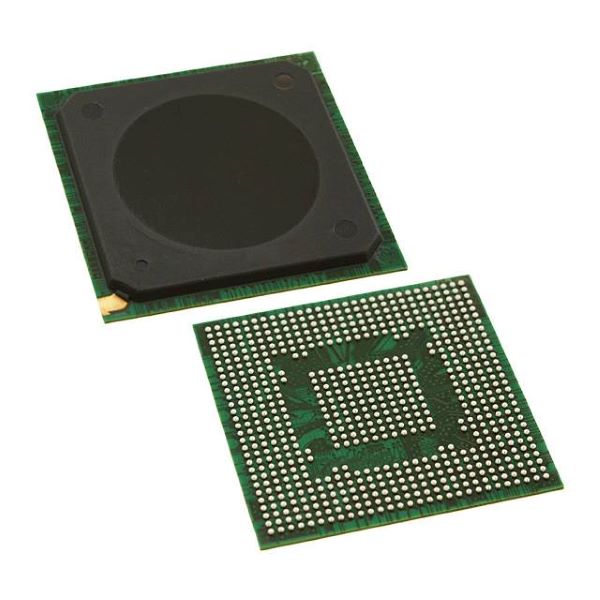

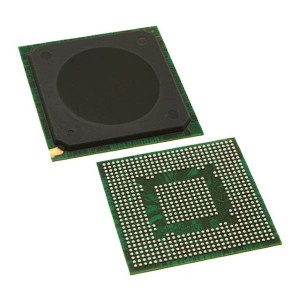

| Pakaĵo/Kesto: | TEPBGA-689 |

| Serio: | P1020 |

| Kerno: | e500 |

| Nombro de Kernoj: | 2 Kerno |

| Larĝo de Datenbuso: | 32-bita |

| Maksimuma Horloĝa Frekvenco: | 800 MHz |

| L1 Kaŝmemora Instrukcia Memoro: | 2 x 32 kB |

| L1 Kaŝmemora Datummemoro: | 2 x 32 kB |

| Funkciiga Proviza Tensio: | 1 V |

| Minimuma Funkciiga Temperaturo: | - 40 °C |

| Maksimuma Funkciiga Temperaturo: | + 125 °C |

| Pakado: | Pleto |

| Marko: | NXP-Semikonduktaĵoj |

| I/O-tensio: | 1,5 V, 1,8 V, 2,5 V, 3,3 V |

| Tipo de instrukcio: | Glitkomo |

| Interfaca Tipo: | Eterreto, I2C, PCIe, SPI, UART, USB |

| L2-kaŝmemora instrukcio / datummemoro: | 256 kilobajtoj |

| Memortipo: | L1/L2 Kaŝmemoro |

| Humideca Sentema: | Jes |

| Nombro de enigoj/eligoj: | 16 Enigo/Eligo |

| Procesora Serio: | QorIQ |

| Produkta Tipo: | Mikroprocesoroj - MPU |

| Fabrikpakaĵa Kvanto: | 27 |

| Subkategorio: | Mikroprocesoroj - MPU |

| Varnomo: | QorIQ |

| Gardhundaj Tempigiloj: | Neniu Gardhunda Tempigilo |

| Parto # Kaŝnomoj: | 935310441557 |

| Unuopezo: | 5.247 gramoj |

• Duoblaj alt-efikecaj 32-bitaj kernoj, konstruitaj sur Power Architecture®-teknologio:

– 36-bita fizika adresado

- Duobla-preciza glitkoma subteno

– 32 Kbajtoj L1 instrukcia kaŝmemoro kaj 32 Kbajtoj L1 datenkaŝmemoro por ĉiu kerno

– horloĝfrekvenco de 533 MHz ĝis 800 MHz

• 256 Kbajtoj L2-kaŝmemoro kun ECC. Ankaŭ agordebla kiel SRAM kaj konserva memoro.

• Tri 10/100/1000 Mbps plibonigitaj tri-rapidaj Eterretaj regiloj (eTSECoj)

– TCP/IP-akcelo, kvalito de servo kaj klasifikkapabloj

– IEEE® 1588 subteno

– Senperda fluokontrolo

– MII, RMII, RGMII, SGMII

• Alt-rapidaj interfacoj subtenantaj diversajn multipleksajn opciojn:

– Kvar SerDes ĝis 2.5 GHz/leno multipleksitaj tra regiloj

– Du PCI Express-interfacoj

– Du SGMII-interfacoj

• Alt-rapida USB-regilo (USB 2.0)

– Subteno por gastigantoj kaj aparatoj

– Plibonigita interfaco de gastiga regilo (EHCI)

– ULPI-interfaco al PHY

• Plibonigita sekura cifereca gastiga regilo (SD/MMC)

• Plibonigita seria periferia interfaco (eSPI)

• Integra sekureca motoro

– Protokola subteno inkluzivas ARC4, 3DES, AES, RSA/ECC, RNG, unu-pasan SSL/TLS

– XOR-akcelo

• 32-bita DDR2/DDR3 SDRAM-memorregilo kun ECC-subteno

• Programebla interrompa regilo (PIC) konforma al la normo OpenPIC

• Unu kvar-kanala DMA-regilo

• Du I2C-regiloj, DUART, tempigiloj

• Plibonigita loka busregilo (eLBC)

• TDM

• 16 ĝeneraluzeblaj enigaj/eligaj signaloj

• Temperaturo de funkcianta krucvojo (Tj): 0–125°C kaj –40°C ĝis 125°C (industria specifo)

• 31 × 31 mm 689-pingla WB-TePBGA II (dratliga temperatur-plibonigita plasta BGA)