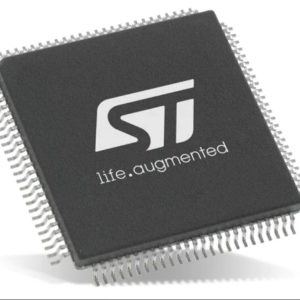

SPC563M64L5COAR 32-bitaj mikroregiloj - MCU 32-BITA Enkonstruita MCU 80 MHz, 1.5 Mbajtoj

♠ Produkta Priskribo

| Produkta Atributo | Atributa Valoro |

| Fabrikisto: | STMicroelectronics |

| Produkta Kategorio: | 32-bitaj mikroregiloj - MCU |

| RoHS: | Detaloj |

| Serio: | SPC563M64L5 |

| Munta Stilo: | SMD/SMT |

| Pakaĵo/Kesto: | LQFP-144 |

| Kerno: | e200z335 |

| Programmemora Grandeco: | 1.5 MB |

| Grandeco de datuma RAM: | 94 kilobajtoj |

| Larĝo de Datenbuso: | 32-bita |

| ADC-Rezolucio: | 2 x 8 bitoj/10 bitoj/12 bitoj |

| Maksimuma Horloĝa Frekvenco: | 80 MHz |

| Nombro de enigoj/eligoj: | 105 Enigo/Eligo |

| Proviza Tensio - Min: | 5 V |

| Proviza Tensio - Maks: | 5 V |

| Minimuma Funkciiga Temperaturo: | - 40 °C |

| Maksimuma Funkciiga Temperaturo: | + 125 °C |

| Kvalifiko: | AEC-Q100 |

| Pakado: | Bobeno |

| Pakado: | Tranĉita Glubendo |

| Pakado: | Musbobeno |

| Marko: | STMicroelectronics |

| Humideca Sentema: | Jes |

| Produkta Tipo: | 32-bitaj mikroregiloj - MCU |

| Fabrikpakaĵa Kvanto: | 500 |

| Subkategorio: | Mikroregiloj - MCU |

| Unuopezo: | 1.290 gramoj |

♠ 32-bita Power Architecture®-bazita mikrokontrolilo por aŭtomobilaj potencotrajnaj aplikoj

Ĉi tiuj 32-bitaj aŭtomobilaj mikroregiloj estas familio de Sistemo-sur-Ĉipa (SoC) aparatoj, kiuj enhavas multajn novajn funkciojn kunligitajn kun alt-efikeca 90 nm CMOS-teknologio por provizi konsiderindan redukton de kosto po funkcio kaj signifan plibonigon de la rendimento. La progresinta kaj kostefika gastiga procesora kerno de ĉi tiu aŭtomobila regilfamilio estas konstruita sur la teknologio Power Architecture®. Ĉi tiu familio enhavas plibonigojn, kiuj plibonigas la taŭgecon de la arkitekturo en enigitajn aplikojn, inkluzivas plian instrukcian subtenon por Cifereca Signal-Prilaborado (DSP), integras teknologiojn - kiel plibonigitan tempan procesoran unuon, plibonigitan vicigitan analog-ciferecan konvertilon, Regilan Arean Reton, kaj plibonigitan modulan enig-eligan sistemon - kiuj gravas por la hodiaŭaj malaltkvalitaj potenco-trajnaj aplikoj. La aparato havas unu-nivelan memorhierarkion konsistantan el ĝis 94 KB sur-ĉipa SRAM kaj ĝis 1.5 MB da interna fulmmemoro. La aparato ankaŭ havas Eksteran Busan Interfacon (EBI) por "alĝustigo".

■ Unuopa eldono, 32-bita Power Architecture® Libro E konforma al e200z335 CPU-kerna komplekso

– Inkluzivas plibonigojn de Variablo-Longkodado (VLE) por redukti la grandecon de kodo

■ 32-kanala rekta memoralira regilo (DMA)

■ Interrompa Regilo (INTC) kapabla pritrakti 364 interrompofontojn kun elektebla prioritato: 191 periferiaj interrompofontoj, 8 softvaraj interrompoj kaj 165 rezervitaj interrompoj.

■ Frekvenc-Modulita Faz-Ŝlosita Buklo (FMPLL)

■ Kalibrada Ekstera Busa Interfaco (EBI)(a)

■ Sistemintegriĝa Unuo (SIU)

■ Ĝis 1,5 Mbajtoj surĉipa fulmmemoro kun fulmregilo

– Akcelilo por unu-cikla fulma aliro je 80 MHz

■ Ĝis 94 Kbajtoj da surĉipa statika RAM (inkluzive de ĝis 32 Kbajtoj da rezerva RAM)

■ Modulo por Helpo al Ekfunkciigo (BAM)

■ 32-kanala duageneracia plibonigita Tempoprocesora Unuo (eTPU)

– 32 normaj eTPU-kanaloj

– Arkitekturaj plibonigoj por plibonigi kodan efikecon kaj aldoni flekseblecon

■ 16-kanala plibonigita Modula Enigo-Eligo-Sistemo (eMIOS)

■ Plibonigita Vicigita Analog-al-Cifereca Konvertilo (eQADC)

■ Malpliiga filtrilo (parto de eQADC)

■ Temperatursensilo de silicia ŝablono

■ 2 Deserial Seria Peripheral Interface (DSPI) moduloj (kongruaj kun Microsecond Bus)

■ 2 plibonigitaj Seria Komunikada Interfaco (eSCI) moduloj kongruaj kun LIN

■ 2 moduloj de Controller Area Network (FlexCAN) kiuj subtenas CAN 2.0B

■ Nexus-Porta Regilo (NPC) laŭ la normo IEEE-ISTO 5001-2003

■ Subteno de IEEE 1149.1 (JTAG)

■ Nexus-interfaco

■ Surĉipa tensioreguligilo, kiu provizas 1,2 V kaj 3,3 V internajn provizojn de 5 V ekstera fonto.

■ Destinita por LQFP144 kaj LQFP176