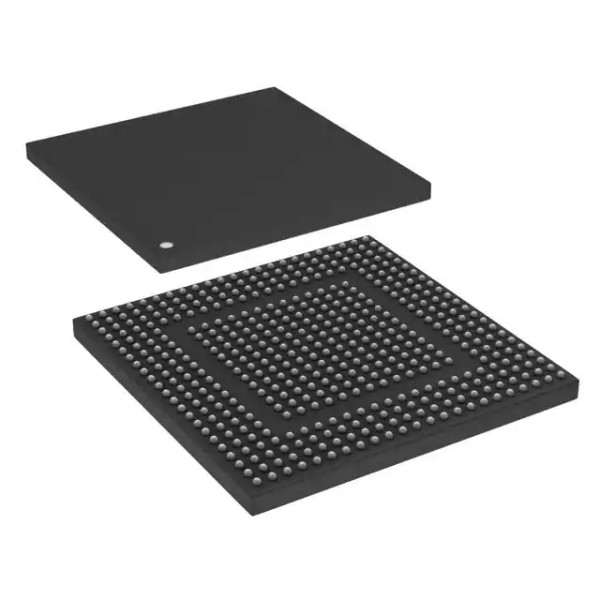

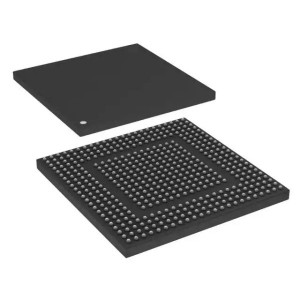

SPC5675KFF0MMS2 32bitaj Mikroregiloj MCU 2MFlash 512KSRAM EBI

♠ Produkta Priskribo

| Produkta Atributo | Atributa Valoro |

| Fabrikisto: | NXP |

| Produkta Kategorio: | 32-bitaj mikroregiloj - MCU |

| RoHS: | Detaloj |

| Serio: | MPC5675K |

| Munta Stilo: | SMD/SMT |

| Pakaĵo / Kazo: | BGA-473 |

| Kerno: | e200z7d |

| Programmemora Grandeco: | 2 MB |

| Grandeco de datuma RAM: | 512 kilobajtoj |

| Larĝo de Datenbuso: | 32-bita |

| ADC-Rezolucio: | 12-bita |

| Maksimuma Horloĝa Frekvenco: | 180 MHz |

| Proviza Tensio - Min: | 1.8 V |

| Proviza Tensio - Maks: | 3.3 V |

| Minimuma Funkciiga Temperaturo: | - 40 °C |

| Maksimuma Funkciiga Temperaturo: | + 125 °C |

| Kvalifiko: | AEC-Q100 |

| Pakado: | Pleto |

| Analoga proviza tensio: | 3.3 V/5 V |

| Marko: | NXP-Semikonduktaĵoj |

| Tipo de datummemorilo: | SRAM |

| I/O-tensio: | 3.3 V |

| Humideca Sentema: | Jes |

| Procesora Serio: | MPC567xK |

| Produkto: | MCU |

| Produkta Tipo: | 32-bitaj mikroregiloj - MCU |

| Programmemora Tipo: | Fulmo |

| Fabrikpakaĵa Kvanto: | 420 |

| Subkategorio: | Mikroregiloj - MCU |

| Gardhundaj Tempigiloj: | Gardhunda Tempigilo |

| Parto # Kaŝnomoj: | 935310927557 |

| Unuopezo: | 0.057260 uncoj |

♠ MPC5675K Mikroregilo

La mikroregilo MPC5675K, solvo de SafeAssure, estas32-bita enigita regilo desegnita por progresinta peliloasistaj sistemoj kun RADAR, CMOS-bildigo, LIDARkaj ultrasonaj sensiloj, kaj multnombraj 3-fazaj motoraj kontrolojaplikoj kiel en hibridaj elektraj veturiloj (HEV) enaŭtomobilaj kaj alttemperaturaj industriaj aplikoj.

Membro de la familio MPC5500/5600 de NXP Semiconductor,ĝi enhavas la Libro E konforman Potencan Arkitekturonteknologia kerno kun Variablo-Longa Kodado (VLE). Ĉi tiokerno konformas al la enigita Power Architecturekategorio, kaj estas 100-procente kongrua kun la uzanto-reĝimooriginala arkitekturo de uzantaj instrukcioj de Power PC™ (UISA).Ĝi ofertas sisteman rendimenton ĝis kvaroblan ol ĝiaAntaŭulo de MPC5561, samtempe alportante al vi la fidindecon kajkonateco de la elprovita teknologio Power Architecture.

Ampleksa aro de aparataro kaj programaroevoluigaj iloj estas haveblaj por helpi simpligi kaj rapidigisistemdezajno. Evoluiga subteno haveblas deĉefaj vendistoj de iloj provizantaj kompililojn, erarserĉilojn kajsimuladaj evoluigaj medioj.

• Alt-efikeca e200z7d duobla kerno

— 32-bita teknologio Power Architecture CPU

— Ĝis 180 MHz kerna frekvenco

— Duobla-tema kerno

— Variablolonga kodado (VLE)

— Memoradministra unuo (MMU) kun 64 enigoj

— 16 KB instrukcia kaŝmemoro kaj 16 KB da datenkaŝmemoro

• Memoro havebla

— Ĝis 2 MB koda fulmmemoro kun ECC

— 64 KB datenfulmmemoro kun ECC

— Ĝis 512 KB surĉipa SRAM kun ECC

• Noviga sekureca koncepto SIL3/ASILD: LockStep-reĝimo kaj erarrezista protekto

— Sfero de replikado (SoR) por ŝlosilaj komponantoj

— Redundaj kontrolaj unuoj ĉe eliroj de la SoR konektita al FCCU

— Unuo por kolektado kaj kontrolado de eraroj (FCCU)

— Enkonstruita memtesto dum la startigo por memoro (MBIST) kaj logiko (LBIST) ekigita de aparataro

— Enkonstruita memtesto dum la startigo por ADC kaj fulmmemoro

— Reproduktita sekurec-plibonigita gardohunda tempigilo

— Temperatursensilo de silicia substrato (ĵetkubo)

— Ne-maskebla interrompo (NMI)

— 16-regiona memora protekta unuo (MPU)

— Horloĝaj monitoraj unuoj (CMU)

— Unuo por administrado de energio (PMU)

— Ciklaj redundanckontrolaj (CRC) unuoj

• Malkuplita Paralela reĝimo por alt-efikeca uzo de reproduktitaj kernoj

• Nexus Klaso 3+ interfaco

• Interrompoj

— Replikita 16-prioritata interromporegilo

• GPIO-oj individue programeblaj kiel enigo, eligo aŭ speciala funkcio

• 3 ĝeneraluzeblaj e-tempigiloj (po 6 kanaloj)

• 3 FlexPWM-unuoj kun kvar 16-bitaj kanaloj po modulo

• Komunikadaj interfacoj

— 4 LINFlex-moduloj

— 3 DSPI-moduloj kun aŭtomata ĉipselekta generado

— 4 FlexCAN-interfacoj (2.0B Aktivaj) kun 32 mesaĝobjektoj

— FlexRay-modulo (V2.1) kun duobla kanalo, ĝis 128 mesaĝobjektoj kaj ĝis 10 Mbit/s

— Rapida Eterreta Regilo (FEC)

— 3 I2C-moduloj

• Kvar 12-bitaj analog-ciferecaj konvertiloj (ADC-oj)

— 22 enigaj kanaloj

— Programebla kruc-ekiga unuo (CTU) por sinkronigi ADC-konverton kun tempigilo kaj PWM

• Ekstera busa interfaco

• 16-bita ekstera DDR-memorregilo

• Paralela cifereca interfaco (PDI)

• Surĉipa CAN/UART-startiga ŝargilo

• Kapabla funkcii per ununura 3,3 V tensioprovizo

— 3,3 V-nur-moduloj: I/O, oscilatoroj, fulmmemoro

— 3,3 V aŭ 5 V moduloj: ADC-oj, provizo al interna VREG

— 1,8–3,3 V provizintervalo: DRAM/PDI

• Temperaturo de funkcianta kunigo -40 ĝis 150 °C