TMS320C6674ACYPA Multicore Fix/Float Pt Dig Sig Proc

♠ Produkta Priskribo

| Produkta Atributo | Atributa Valoro |

| Fabrikisto: | Teksasaj Instrumentoj |

| Produkta Kategorio: | Ciferecaj Signalprocesoroj kaj Regiloj - DSP, DSC |

| Produkto: | DSP-oj |

| Serio: | TMS320C6674 |

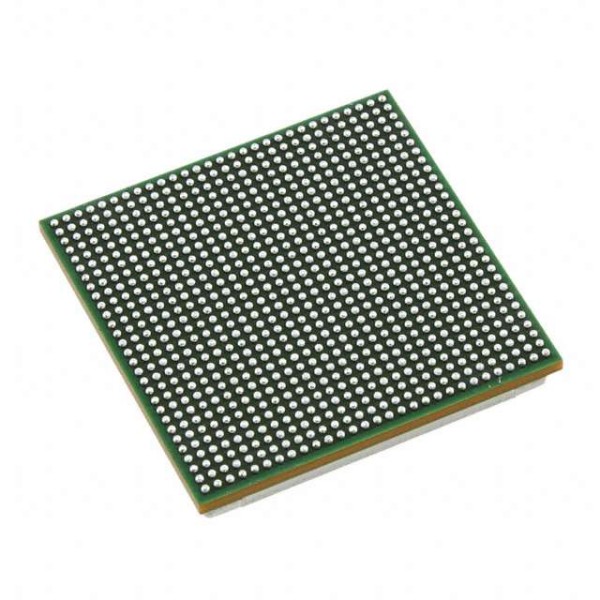

| Munta Stilo: | SMD/SMT |

| Pakaĵo / Kazo: | FCBGA-841 |

| Kerno: | C66x |

| Nombro de Kernoj: | 4 Kerno |

| Maksimuma Horloĝa Frekvenco: | 1 GHz, 1.25 GHz |

| L1 Kaŝmemora Instrukcia Memoro: | 4 x 32 kB |

| L1 Kaŝmemora Datummemoro: | 4 x 32 kB |

| Programmemora Grandeco: | - |

| Grandeco de datuma RAM: | - |

| Funkciiga Proviza Tensio: | 900 mV ĝis 1.1 V |

| Minimuma Funkciiga Temperaturo: | - 40 °C |

| Maksimuma Funkciiga Temperaturo: | + 100 °C |

| Pakado: | Pleto |

| Marko: | Teksasaj Instrumentoj |

| Larĝo de Datenbuso: | 8 bitoj/16 bitoj/32 bitoj |

| Tipo de instrukcio: | Fiksa/Glaŭkoma |

| MMACS: | 160000 MMACS |

| Humideca Sentema: | Jes |

| Nombro de enigoj/eligoj: | 16 Enigo/Eligo |

| Nombro de Tempigiloj/Nombriloj: | 12 Tempigilo |

| Produkta Tipo: | DSP - Ciferecaj Signalprocesoroj kaj Regiloj |

| Fabrikpakaĵa Kvanto: | 44 |

| Subkategorio: | Enkonstruitaj procesoroj kaj regiloj |

| Proviza Tensio - Maks: | 1.1 V |

| Proviza Tensio - Min: | 900 mV |

| Unuopezo: | 0.173396 uncoj |

♠ Multkerna Fiksa kaj Glitkoma Cifereca Signalprocesoro

La TMS320C6674 DSP estas plej alt-efikeca fiksa/glitkoma DSP bazita sur la multkerna arkitekturo KeyStone de TI. Enkorpigante la novan kaj novigan C66x DSP-kernon, ĉi tiu aparato povas funkcii je kerna rapido ĝis 1.25 GHz. Por programistoj de vasta gamo da aplikoj, kiel ekzemple misi-kritikaj sistemoj, medicina bildigo, testado kaj aŭtomatigo, kaj aliaj aplikoj postulantaj altan rendimenton, la TMS320C6674 DSP de TI ofertas 5 GHz-akumulan DSP kaj ebligas platformon, kiu estas energiefika kaj facile uzebla. Krome, ĝi estas plene retrokongrua kun ĉiuj ekzistantaj fiksaj kaj glitkomaj DSP-oj de la C6000-familio.

La arkitekturo KeyStone de TI provizas programeblan platformon integrantan diversajn subsistemojn (C66x-kernoj, memorsubsistemo, flankaparatoj kaj akceliloj) kaj uzas plurajn novigajn komponantojn kaj teknikojn por maksimumigi intra-aparatan kaj inter-aparatan komunikadon, kiu permesas al la diversaj DSP-resursoj funkcii efike kaj senjunte. Centraj al ĉi tiu arkitekturo estas ŝlosilaj komponantoj kiel Multicore Navigator, kiu ebligas efikan datumadministradon inter la diversaj aparataj komponantoj. La TeraNet estas ne-bloka ŝaltilŝtofo, kiu ebligas rapidan kaj disput-liberan internan datummovadon. La multkerna komuna memorregilo permesas aliron al komuna kaj ekstera memoro rekte sen ĉerpi el la kapacito de la ŝaltilŝtofo.

• Kvar TMS320C66x™ DSP-kernaj subsistemoj (C66x CorePacs), ĉiu kun

– 1.0 GHz aŭ 1.25 GHz C66x Fiksa/Gltkoma CPU-Kerno

› 40 GMAC/Kerno por Fiksa Punkto je 1.25 GHz

› 20 GFLOP/Kerno por Glitkoma je 1.25 GHz

– Memoro

› 32K bajtoj L1P po kerno

› 32K bajtoj L1D po kerno

› 512K bajtoj loka L2 po kerno

• Multkerna Kunhavata Memorregilo (MSMC)

– 4096KB MSM SRAM-memoro kunhavita de kvar DSP C66x CorePac-oj

– Memorprotekta Unuo por Kaj MSM SRAM Kaj DDR3_EMIF

• Multkerna Navigilo

– 8192 Multcelaj Aparataj Atendovicoj kun Atendovic-Administrilo

– Pakaĵ-bazita DMA por nul-supraj translokigoj

• Reta Kunprocesoro

– Pakaĵa Akcelilo Ebligas Subtenon por

› Transporta aviadilo IPsec, GTP-U, SCTP, PDCP

› L2 Uzanto-Ebeno PDCP (RoHC, Aera Ĉifrado)

› 1-Gbps dratrapida trairo je 1.5 MPakaĵoj po sekundo

– Sekureca Akcelilo Ebligas Subtenon por

› IPSec, SRTP, 3GPP, WiMAX Aera Interfaco, kaj SSL/TLS Sekureco

› ECB, CBC, CTR, F8, A5/3, CCM, GCM, HMAC, CMAC, GMAC, AES, DES, 3DES, Kasumi, SNOW 3G, SHA-1, SHA-2 (256-bita Haŝo), MD5

› Ĝis 2.8 Gbps Ĉifrada Rapido

• Flankaj aparatoj

– Kvar Lenoj de SRIO 2.1

› 1.24/2.5/3.125/5 GBaud-operacio subtenata po leno

› Subtenas rektan enigon/eligon, mesaĝan transdonon

› Subtenas kvar 1×, du 2×, unu 4×, kaj du 1× + unu 2× ligokonfiguraciojn

– PCIe Gen2

› Unuopa Haveno Subtenanta 1 aŭ 2 Lenojn

› Subtenas Ĝis 5 GBaŭdojn Po Leno

– Hiperligo

› Subtenas Konektojn al Aliaj KeyStone Arkitekturaj Aparatoj Provizante Rimedan Skaleblecon

› Subtenas ĝis 50 Gbaŭdojn

– Gigabit Ethernet (GbE) Ŝaltilsubsistemo

› Du SGMII-havenoj

› Subtenas funkciadon de 10/100/1000 Mbps

– 64-bita DDR3-interfaco (DDR3-1600)

› 8G-bajta adresebla memorspaco

– 16-bita EMIF

– Du Telekomunikaj Seriaj Datumoj (TSIP)

› Subtenas 1024 DS0-ojn por TSIP

› Subtenas 2/4/8 lenojn je 32.768/16.384/8.192 Mbps po leno

– UART-interfaco

– I²C-interfaco

– 16 GPIO-stiftoj

– SPI-interfaco

– Semafora Modulo

– Dek du 64-bitaj tempigiloj

– Tri surĉipaj PLL-oj

• Komerca Temperaturo:

– 0°C ĝis 85°C

• Plilongigita Temperaturo:

– -40°C ĝis 100°C

• Misio-Kritikaj Sistemoj

• Alt-efikecaj Komputilaj Sistemoj

• Komunikadoj

• Aŭdio

• Videa Infrastrukturo

• Bildigo

• Analizo

• Retigado

• Amaskomunikila Prilaborado

• Industria Aŭtomatigo

• Aŭtomatigo kaj Proceza Kontrolo