XC6SLX75-2FGG484C Kampe Programebla Pordega Aro

♠ Produkta Priskribo

| Produkta Atributo | Atributa Valoro |

| Fabrikisto: | Xilinx |

| Produkta Kategorio: | FPGA - Kampe Programebla Pordega Aro |

| RoHS: | Detaloj |

| Serio: | XC6SLX75 |

| Nombro de Logikaj Elementoj: | 74637 LE |

| Nombro de enigoj/eligoj: | 280 Enigo/Eligo |

| Proviza Tensio - Min: | 1.14 V |

| Proviza Tensio - Maks: | 1.26 V |

| Minimuma Funkciiga Temperaturo: | 0 °C |

| Maksimuma Funkciiga Temperaturo: | + 85 °C |

| Datumrapideco: | - |

| Nombro de Sensiloj: | - |

| Munta Stilo: | SMD/SMT |

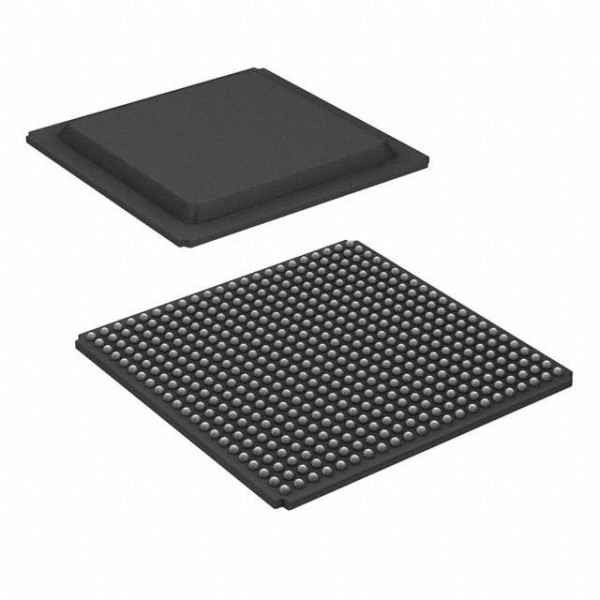

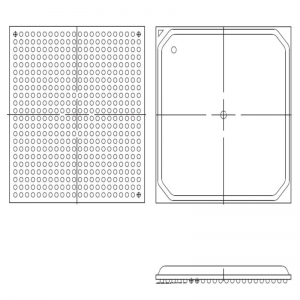

| Pakaĵo / Kazo: | FCBGA-484 |

| Marko: | Xilinx |

| Distribuita RAM: | 692 kbitoj |

| Enkonstruita Bloka RAM - EBR: | 3096 kbitoj |

| Maksimuma Funkciiga Frekvenco: | 1080 MHz |

| Humideca Sentema: | Jes |

| Nombro de Logikaj Aro-Blokoj - LAB-oj: | 5831 LABORATORIO |

| Funkciiga Proviza Tensio: | 1.2 V |

| Produkta Tipo: | FPGA - Kampe Programebla Pordega Aro |

| Fabrikpakaĵa Kvanto: | 1 |

| Subkategorio: | Programeblaj Logikaj IC-oj |

| Varnomo: | Spartana |

| Unuopezo: | 1.662748 uncoj |

♠ Superrigardo de la Spartan-6 Familio

La familio Spartan®-6 provizas ĉefajn kapablojn pri sistema integriĝo kun la plej malalta totala kosto por grandvolumenaj aplikoj. La dektri-membra familio liveras pligrandigitajn densecojn intervalantajn de 3 840 ĝis 147 443 logikaj ĉeloj, kun duono de la energikonsumo de antaŭaj Spartan-familioj, kaj pli rapidan, pli ampleksan konekteblecon. Konstruita sur matura 45 nm malalt-energia kupra procezteknologio, kiu liveras la optimuman ekvilibron inter kosto, energikonsumo kaj rendimento, la familio Spartan-6 ofertas novan, pli efikan, duoble-registran 6-enigan serĉtabelan (LUT) logikon kaj riĉan elekton de enkonstruitaj sistemnivelaj blokoj. Ĉi tiuj inkluzivas 18 Kb (2 x 9 Kb) blokajn RAM-ojn, duageneraciajn DSP48A1-tranĉaĵojn, SDRAM-memorregilojn, plibonigitajn miksreĝimajn horloĝadministradajn blokojn, SelectIO™-teknologion, energi-optimumigitajn altrapidajn seriajn sendricevilajn blokojn, PCI Express®-kongruajn finpunktajn blokojn, progresintajn sistemnivelajn energiadministradajn reĝimojn, aŭtomatajn detektajn agordajn opciojn kaj plibonigitan IP-sekurecon kun AES kaj Device DNA-protekto.

Ĉi tiuj trajtoj provizas malaltkostan programeblan alternativon al kutimaj ASIC-produktoj kun senprecedenca facileco de uzo. Spartan-6 FPGA-oj ofertas la plej bonan solvon por grandvolumenaj logikaj dezajnoj, konsumant-orientitaj DSP-dezajnoj kaj kost-sentemaj enigitaj aplikoj. Spartan-6 FPGA-oj estas la programebla silicia fundamento por Celitaj Dezajnaj Platformoj, kiuj liveras integrajn programarajn kaj aparatarajn komponantojn, kiuj ebligas al dizajnistoj fokusiĝi pri novigado tuj kiam ilia disvolva ciklo komenciĝas.

• Spartan-6 Familio:

- Spartan-6 LX FPGA: Logike optimumigita

- Spartan-6 LXT FPGA: Alt-rapida seria konektebleco

• Dizajnita por malalta kosto

- Multoblaj efikaj integraj blokoj

- Optimumigita elekto de I/O-normoj

- Ŝanceligitaj kusenetoj

- Grandvolumenaj plastaj drat-ligitaj pakaĵoj

• Malalta statika kaj dinamika potenco

- 45-nm procezo optimumigita por kosto kaj malalta potenco

- Reĝimo de vintrodormo por malŝalto de nula energio

- Suspenda reĝimo konservas staton kaj agordon per plurstifta vekiĝo, plibonigo de kontrolo

- Malpli potenca 1.0V kerna tensio (LX FPGA-oj, nur -1L)

- Alta rendimento 1.2V kerna tensio (LX kaj LXT FPGA-oj, -2, -3, kaj -3N rapidgradoj)

• Multtensiaj, multnormaj SelectIO™ interfacaj bankoj

- Ĝis 1,080 Mb/s datumtransiga rapido por ĉiu diferenciala I/O

- Elektebla elira stirado, ĝis 24 mA po pinglo

- Normoj kaj protokoloj de 3.3V ĝis 1.2VI/O

- Malaltkostaj HSTL kaj SSTL memorinterfacoj

- Varma interŝanĝa plenumo

- Alĝustigeblaj I/O-ŝanĝrapidecoj por plibonigi signalintegrecon

• Alt-rapidaj GTP-seriaj transceivoj en la LXT FPGA-oj

- Ĝis 3.2 Gb/s

- Alt-rapidaj interfacoj inkluzive de: Seria ATA, Aurora, 1G Eterreto, PCI Express, OBSAI, CPRI, EPON, GPON, DisplayPort, kaj XAUI

• Integra finpunkta bloko por PCI Express-dezajnoj (LXT)

• Malaltkosta subteno de PCI®-teknologio kongrua kun la specifoj de 33 MHz, 32- kaj 64 bitoj.

• Efikaj DSP48A1-tranĉaĵoj

- Alt-efikeca aritmetiko kaj signal-prilaborado

- Rapida 18 x 18 multiplikilo kaj 48-bita akumulilo

- Duktosistemo kaj kaskada kapablo

- Antaŭ-aldonaĵo por helpi filtrilaplikojn

• Integraj Memorregilaj blokoj

- Subteno por DDR, DDR2, DDR3, kaj LPDDR

- Datenrapidecoj ĝis 800 Mb/s (12.8 Gb/s pinta bendolarĝo)

- Multporta busstrukturo kun sendependa FIFO por redukti dezajntempajn problemojn

• Abundaj logikaj rimedoj kun pliigita logika kapacito

- Laŭvola ŝovregistro aŭ distribuita RAM-subteno

- Efikaj 6-enigaj LUT-oj plibonigas rendimenton kaj minimumigas potencon

- LUT kun duoblaj flip-flops por dukto-centraj aplikoj

• Bloka RAM kun vasta gamo de granuleco

- Rapida bloka RAM kun bajta skrib-ebligilo

- 18 Kb blokoj kiuj povas esti laŭvole programitaj kiel du sendependaj 9 Kb blokaj RAM-oj

• Horloĝa Administra Kahelo (CMT) por plibonigita rendimento

- Malbrua, fleksebla horloĝado

- Ciferecaj Horloĝmanaĝeroj (DCM-oj) forigas horloĝan misprezenton kaj impostciklan misprezenton

- Faz-Ŝlositaj Bukloj (PLL-oj) por malalt-jitter-horloĝado

- Frekvencsintezo kun samtempa multipliko, divido kaj fazoŝovo

- Dek ses malalt-misoblikvaj tutmondaj horloĝretoj

• Simpligita agordo, subtenas malaltkostajn normojn

- 2-pingla aŭtomata detekta agordo

- Larĝa triaparta SPI (ĝis x4) kaj NOR-fulmsubteno

- Funkcioriĉa Xilinx Platform Flash kun JTAG

- Subteno de MultiBoot por fora ĝisdatigo kun pluraj pecfluoj, uzante gardohundoprotekton

• Plibonigita sekureco por dezajna protekto

- Unika Aparata DNA-identigilo por dezajna aŭtentikigo

- AES-bitflua ĉifrado en la pli grandaj aparatoj

• Pli rapida enigita prilaborado kun plibonigita, malaltkosta, MicroBlaze™ mola procesoro

• Industri-gvidaj IP- kaj referencaj dezajnoj