LCMXO1200C-3TN144I FPGA – Kampe Programebla Pordega Aro 1200 LUT-oj 113 IO 1.8 /2.5/3.3V -3 Spd I

♠ Produkta Priskribo

| Produkta Atributo | Atributa Valoro |

| Fabrikisto: | Krado |

| Produkta Kategorio: | FPGA - Kampe Programebla Pordega Aro |

| RoHS: | Detaloj |

| Serio: | LCMXO1200C |

| Nombro de Logikaj Elementoj: | 1200 leoj |

| Nombro de enigoj/eligoj: | 113 Enigo/Eligo |

| Proviza Tensio - Min: | 1.71 V |

| Proviza Tensio - Maks: | 3.465 Voltoj |

| Minimuma Funkciiga Temperaturo: | - 40 °C |

| Maksimuma Funkciiga Temperaturo: | + 100 °C |

| Datumrapideco: | - |

| Nombro de Sensiloj: | - |

| Munta Stilo: | SMD/SMT |

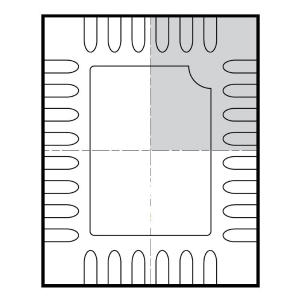

| Pakaĵo/Kesto: | TQFP-144 |

| Pakado: | Pleto |

| Marko: | Krado |

| Distribuita RAM: | 6.4 kbitoj |

| Enkonstruita Bloka RAM - EBR: | 9.2 kbitoj |

| Alto: | 1.4 milimetroj |

| Longo: | 20 milimetroj |

| Maksimuma Funkciiga Frekvenco: | 500 MHz |

| Humideca Sentema: | Jes |

| Nombro de Logikaj Aro-Blokoj - LAB-oj: | 150 LABORATORIO |

| Funkciiga Proviza Kurento: | 21 mA |

| Funkciiga Proviza Tensio: | 1,8 V/2,5 V/3,3 V |

| Produkta Tipo: | FPGA - Kampe Programebla Pordega Aro |

| Fabrikpakaĵa Kvanto: | 60 |

| Subkategorio: | Programeblaj Logikaj IC-oj |

| Totala Memoro: | 15.6 kbitoj |

| Larĝo: | 20 milimetroj |

| Unuopezo: | 1.319 gramoj |

Ne-volatila, Senlime Reagordebla

• Tujŝaltita - ŝaltiĝas post mikrosekundoj

• Unuopa ĉipo, neniu ekstera agorda memoro necesas

• Bonega dezajna sekureco, neniu bitfluo por interkapti

• Rekonfiguri SRAM-bazitan logikon en milisekundoj

• SRAM kaj nevolatila memoro programeblaj per JTAG-pordo

• Subtenas fonan programadon de nevolatila memoro

Dormreĝimo

• Permesas ĝis 100-oblan redukton de statika kurento

TransFR™ Rekonfiguracio (TFR)

• Ĝisdatigo de logika enkampo dum la sistemo funkcias

Alta I/O al Logika Denseco

• 256 ĝis 2280 LUT4-oj

• 73 ĝis 271 enigoj/eligoj kun ampleksaj pakaĵaj opcioj

• Denseca migrado subtenata

• Senplumba/RoHS-konforma pakaĵo

Enkonstruita kaj Distribuita Memoro

• Ĝis 27.6 Kbitoj sysMEM™ Enkonstruita Bloka RAM

• Ĝis 7.7 Kbitoj da distribuita RAM

• Dediĉita FIFO-kontrollogiko

Fleksebla I/O-Bufro

• Programebla sysIO™-bufro subtenas vastan gamon da interfacoj:

– LVCMOS 3.3/2.5/1.8/1.5/1.2

– LVTTL

– PCI

– LVDS, Bus-LVDS, LVPECL, RSDS

sysCLOCK™ PLL-oj

• Ĝis du analogaj PLL-oj por aparato

• Horloĝa multipliko, divido kaj fazoŝovo

Sistemnivela Subteno

• IEEE-Normo 1149.1 Limskanado

• Enkonstruita oscilatoro

• Aparatoj funkcias kun elektrofonto de 3,3V, 2,5V, 1,8V aŭ 1,2V

• IEEE 1532-kongrua ensistema programado