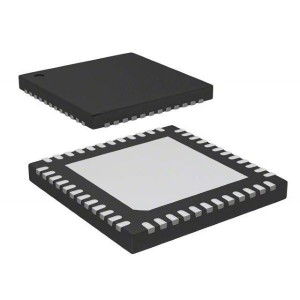

LCMXO640C-4TN144C FPGA - Kampa Programebla Pordega Tablo 640 LUTS 113 I/O

♠ Produkta Priskribo

| Produkta Atributo | Atributa Valoro |

| Fabrikisto: | Krado |

| Produkta Kategorio: | FPGA - Field Programable Gate Array |

| RoHS: | Detaloj |

| Serio: | LCMXO640C |

| Nombro de Logikaj Elementoj: | 640 LE |

| Nombro da I/Oj: | 113 I/O |

| Provizo-tensio - Min: | 1.71 V |

| Proviza Tensio - Maksimuma: | 3.465 V |

| Minimuma Operacia Temperaturo: | 0 C |

| Maksimuma Funkcia Temperaturo: | + 85 C |

| Datumkurso: | - |

| Nombro da Transriceviloj: | - |

| Monta Stilo: | SMD/SMT |

| Pako/Kazo: | TQFP-144 |

| Pakado: | Pleto |

| Marko: | Krado |

| Distribuita RAM: | 6,1 kbit |

| Alteco: | 1,4 mm |

| Longo: | 20 mm |

| Maksimuma Operacia Ofteco: | 550 MHz |

| Sentema al humideco: | Jes |

| Nombro de Logika Tabelo-Blokoj - LABoj: | 80 LAB |

| Funkcia Proviza Kurento: | 17 mA |

| Funkcia Proviza Tensio: | 1.8 V/2.5 V/3.3 V |

| Produkta Tipo: | FPGA - Field Programable Gate Array |

| Fabrika Pako Kvanto: | 60 |

| Subkategorio: | Programeblaj Logikaj ICoj |

| Tuta Memoro: | 6,1 kbit |

| Larĝo: | 20 mm |

| Unueca pezo: | 1.319 g |

Ne-volatila, Senfine Reagordebla

• Instant-on - ŝaltas en mikrosekundoj

• Ununura blato, ne necesas ekstera agorda memoro

• Bonega dezajno sekureco, neniu bitfluo por interkapti

• Reagordu SRAM bazitan logikon en milisekundoj

• SRAM kaj nevolatila memoro programebla per JTAG-haveno

• Subtenas fonan programadon de nevolatila memoro

Dorma Reĝimo

• Permesas ĝis 100x statika nuna redukto

TransFR™ Reagordo (TFR)

• En-kampa logika ĝisdatigo dum sistemo funkcias

Alta I/O al Logika Denso

• 256 ĝis 2280 LUT4-oj

• 73 ĝis 271 I/Os kun ampleksaj pakaĵelektoj

• Denso migrado subtenata

• Senplumbo/RoHS-konforma pakado

Enigita kaj Distribuita Memoro

• Ĝis 27.6 Kbitoj sysMEM™ Embedded Block RAM

• Ĝis 7,7 Kbitoj distribuita RAM

• Dediĉita FIFO-kontrola logiko

Fleksebla I/O Buffer

• Programebla sysIO™-bufro subtenas larĝan gamon de interfacoj:

– LVCMOS 3.3/2.5/1.8/1.5/1.2

– LVTTL

– PCI

– LVDS, Bus-LVDS, LVPECL, RSDS

sysCLOCK™ PLL-oj

• Ĝis du analogaj PLL-oj per aparato

• Horloĝo multobligi, dividi kaj fazŝanĝo

Sistemnivela Subteno

• IEEE Standard 1149.1 Boundary Scan

• Enŝipe oscilatoro

• Aparatoj funkcias per 3.3V, 2.5V, 1.8V aŭ 1.2V elektroprovizo

• IEEE 1532 konforma en-sistema programado